Готов «небрежный» процессор

Если позволить процессорам допускать ошибки в вычислениях, их энергопотребление многократно снизится, определив более длительную автономность.

Мобильные устройства, нуждающиеся в ежедневной подзарядке, смогли бы подпитывать батареи лишь раз в месяц в том случае, если в них использовались бы микросхемы нового типа, работающие с мощностью в одну тридцатую от обычных и в семь раз быстрее за счет системной логики, допускающей возникающие ошибки.

Подобные микросхемы — идеальный выбор для устройств с автономным питанием с приложениями, не требующими 100-процентной точности результатов своей работы. К последним относится потоковое видео на мобильном телефоне. Так, с целью экономии энергии проблемно-ориентированная интегральная микросхема (Application-Specific Integrated Circuit, ASIC) обеспечит генерирование видеопросмотра достаточного качества, но с некоторыми искажениями, которые будут компенсированы человеческой способностью бессознательно додумывать возможные информационные потери.

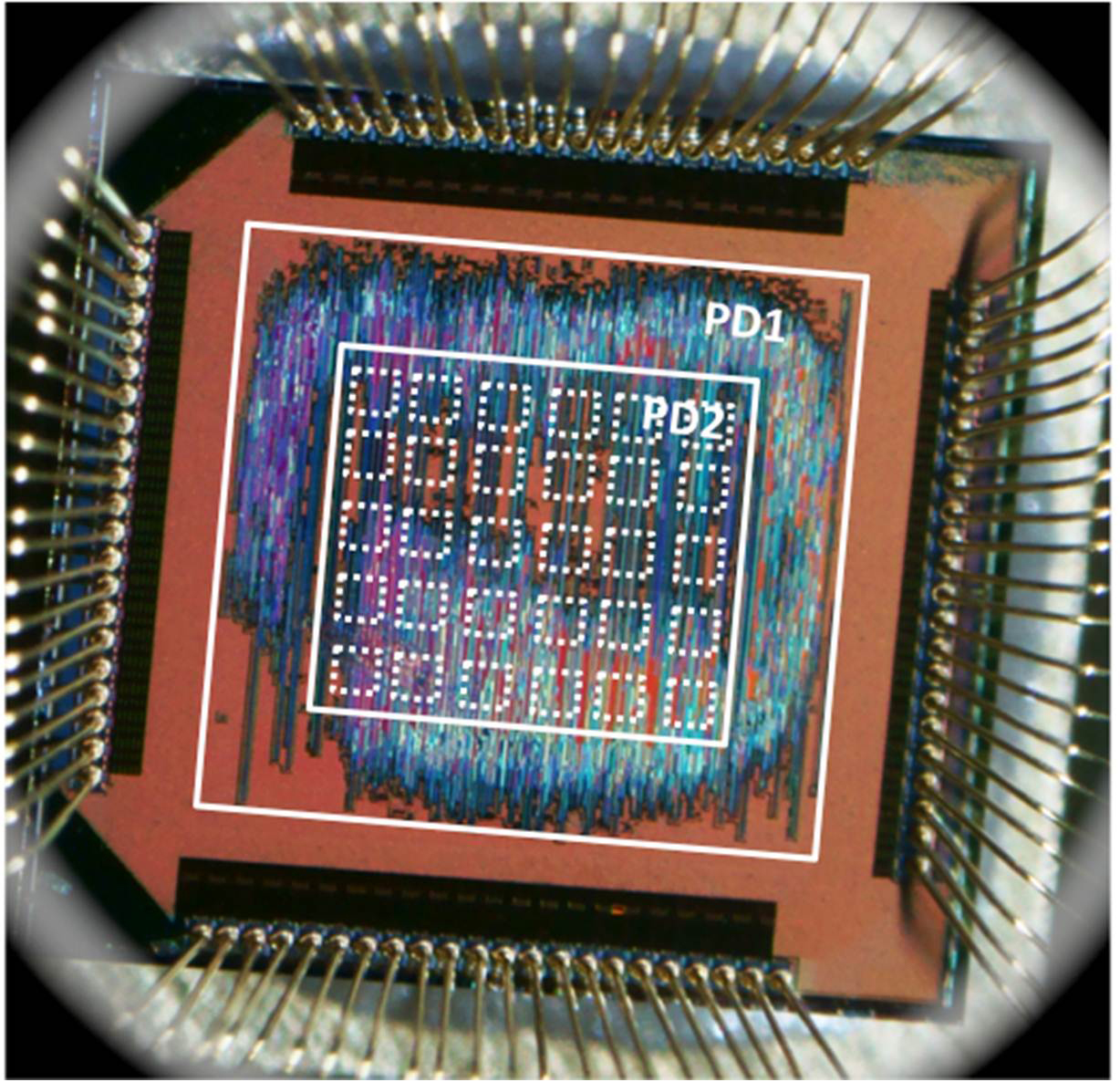

Технология производства так называемых вероятностных комплементарных металлооксидных полупроводников (Probabilistic Complementary Metal-Oxide Semiconductor, PCMOS) разработана командой ученых под руководством профессоров Кришны Паема из Университета Райса (США) и Ео Киат Сэна из Наньянского технологического университета (Сингапур) с привлечением экспертов из Центра электроники и микротехнологий (Швейцария) и Калифорнийского университета в Беркли. Исследования финансировалась Агентством перспективных исследований министерства обороны США (DARPA) и Intel. Выход на рынок ожидается к 2013 году в составе образовательных индийских планшетов iSlate.

Вместо использования булевой логики, лежащей в основе обычных микросхем, PCMOS построены на вероятностной логике, которая менее чувствительна к усиливающимся по мере уменьшения размеров чипа собственным электрическим помехам. В обычных микросхемах поступающий на вход сигнал имеет повышенную мощность с целью подавления шумов. Соответственно, хоть PCMOS и используют гораздо меньше энергии, вероятностной логике приходится учитывать ошибки в результате искажений от смешения сигнала с помехами.

С точки зрения скорости, энергопотребления и размеров «неточные» процессоры в 15 раз эффективнее традиционных. Применен комплексный подход, задействовавший интеллектуальное управление вероятностью ошибок, определяющий, какие именно задачи могут быть неточными, эксплуатирующий процедуру изъятия из проекта процессора редко используемых цифровых схем, а также ограничивающий масштабирование напряжения.

© СОТОВИК